구)홈페이지 오탈자 보기

임베디드 하드웨어 이해와 설계(개정판)

| 장 | 페이지 | 오탈자 내용 | 등록일 | 쇄 |

|---|---|---|---|---|

| 1 | 34 | ((p 34) 두번째 문단 그림 밑에 둘째줄) SDRAM | 2006-11-19 | 1 |

| 2 | 57 | (p 57 - 어셈블리로 코드 작성하기 2번째 문단 ) ""#" -> "#" | 2006-11-19 | 1 |

| 2 | 66 | (66쪽 10줄) 증가/감소하여 -> 감소/증가하여 | 2007-06-30 | 1 |

| 4 | 94 | (94쪽 8줄) 방향을 -> 방식을 | 2007-06-30 | 1 |

| 4 | 101 | (101p 그림 4-10) A0:A3 포트는 이 시트로 들어오는 입력버스이다(즉, 다른 시트에서 나오는 출력이다). | 2006-11-09 | 1 |

| 4 | 120 | (120쪽 8-10줄) 이차 코일로 인해 일차 코일의 전압이 높아지면, 이차코일의 전류는 일차 코일에 비해 그만큼 적어진다. | 2007-06-30 | 1 |

| 4 | 126 | (126쪽 클록과 발진기 첫문단 4,5줄, 둘쨰문단 첫줄) 클록 주기 -> 클록 주파수 | 2007-06-30 | 1 |

| 4 | 133 | (133p. 4번째 단락 셋째줄) 칩은 이보다 더 놓은 온도에서... | 2006-12-04 | 1 |

| 6 | 192 | (p 192 - 3번째 문단 6번째 줄, 7번째 줄) 금속 조각으로 케이블 단자의 2번핀과 3번핀을 단선시킨다. | 2006-11-19 | 1 |

| 7 | 200 | (p200, p201) 1. 그림7-5 아래의 내용. | 2013-02-20 | 6 |

| 7 | 200 | (p.201, p.202) 그림이 서로 같지는 않고, 그림 제목의 오탈자 오류입니다. | 2014-06-16 | 6 |

| 8 | 217 | (p216 두번재 문단 중) "주소바이트는 7비트 주소를 포함하며, 방향 비트 뒤에 나온다." | 2007-07-11 | 1 |

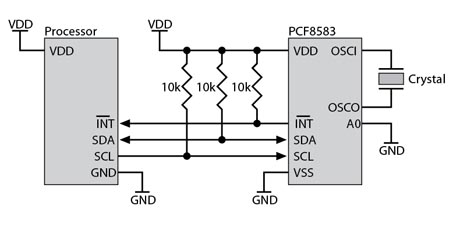

| 8 | 218 | (218) 그림 8-9에 맞는 이미지입니다.

| 2008-08-04 | 2 |

| 13 | 277 | (p 277 3번째 문단 4, 6, 7, 8 줄) 레지스터라는 단어를 사용하였는데, 이 단어는 영어로 'Resistor'입니다. 저항이라고 번역하는 것이 좋습니다. | 2006-11-19 | 1 |

| 18 | 393 | (p 394 주석) 모토롤라 반도체는 이제 프리스케일 반도이다. | 2006-11-19 | 1 |